Cambridge University Press 978-1-107-41219-4 - Materials Research Society Symposium Proceedings: Volume 670: Gate Stack and Silicide Issues in Silicon Processing II Editors: S. A. Campbell, L. A. Clevenger, P. B. Griffin and C. C. Hobbs Excerpt More information

High-k Materials

Cambridge University Press 978-1-107-41219-4 - Materials Research Society Symposium Proceedings: Volume 670: Gate Stack and Silicide Issues in Silicon Processing II Editors: S. A. Campbell, L. A. Clevenger, P. B. Griffin and C. C. Hobbs Excerpt

More information

978-1-107-41219-4 - Materials Research Society Symposium Proceedings: Volume 670:

Gate Stack and Silicide Issues in Silicon Processing II

Editors: S. A. Campbell, L. A. Clevenger, P. B. Griffin and C. C. Hobbs

Excerpt

More information

Mat. Res. Soc. Symp. Proc. Vol. 670 @ 2001 Materials Research Society

## Materials and Physical Properties of Novel High-k and Medium-k Gate Dielectrics

Ran Liu, Stefan Zollner, Peter Fejes, Rich Gregory, Shifeng Lu, Kim Reid, David Gilmer, Bich-Yen Nguyen

DigitalDNA Laboratories, Motorola,

Mesa, AZ 85202, USA

Zhiyi Yu, Ravi Droopad, Jay Curless, Alex Demkov, Jeff Finder, Kurt Eisenbeiser

Physical Science Research Laboratories, Motorola,

Tempe, AZ 85202, USA

## **ABSTRACT**

Rapid shrinking in device dimensions calls for replacement of SiO<sub>2</sub> by new gate insulators in future generations of MOSFETs. Among many desirable properties, potential candidates must have a higher dielectric constant, low leakage current, and thermal stability against reaction or diffusion to ensure sharp interfaces with both the substrate Si and the gate metal (or poly-Si). Extensive characterization of such materials in thin-film form is crucial not only for selection of the alternative gate dielectrics and processes, but also for development of appropriate metrology of the high-k films on Si. This paper will report recent results on structural and compositional properties of thin film SrTiO<sub>3</sub> and transition metal oxides (ZrO<sub>2</sub> and HfO<sub>2</sub>).

## INTRODUCTION

The continued shrinking of the CMOS device size for higher speed and lower power consumption drives the conventional SiO<sub>2</sub> gate oxide approaching its thickness scaling limit [1]. Severe direct tunneling and reliability problems at extremely small thickness will soon set a barrier for this naturally given material. Alternative dielectric materials with a higher dielectric constant, k, and thus larger physical thickness than SiO<sub>2</sub> will be required to reduce the gate leakage as the gate length is scaled below 100 nm. Successful integration of high-k dielectrics into CMOS technology poses enormous challenges. Among many desirable properties, potential candidates must have a higher dielectric constant, low leakage current, and thermal stability against intermixing or diffusion to ensure sharp interfaces with both the substrate Si and the gate metal (or poly-Si). Extensive characterization of such materials in thin-film form is crucial not only for selection of the alternative gate dielectrics and processes, but also for development of appropriate metrology of the high-k films on Si.

For insulating materials, there are two major contributions to the static dielectric function

$$\varepsilon_0 = 1 + 4\pi (\chi_{electron} + \chi_{lattice}), \tag{1}$$

i.e., the dielectric responses of valence electrons and lattice vibrations. The electronic dielectric constant can be estimated by

$$\chi_{electron} \sim \left(\frac{\hbar \omega_P}{E_{PG}}\right)^2,$$

(2)

978-1-107-41219-4 - Materials Research Society Symposium Proceedings: Volume 670:

Gate Stack and Silicide Issues in Silicon Processing II

Editors: S. A. Campbell, L. A. Clevenger, P. B. Griffin and C. C. Hobbs

Excerpt

More information

where  $\omega_{r}$  is the plasma frequency of the valence electrons and  $E_{rg}$  is an "average bandgap" (know as Penn gap). Since the electronic contribution is usually less than 16 and larger for insulators with smaller energy gaps, it is not wise to pursue materials with high electronic dielectric constant as high-k gate dielectrics. Therefore, the high dielectric constant should be generated from the ionic contribution

$$\chi_{lattice} \sim \frac{1}{V} \sum_{i} \frac{\left(e_{i}^{*} \cdot \xi_{i}\right) \left(e_{i}^{*} \cdot \xi_{i}\right)^{+}}{\omega_{i}^{2}}, \tag{3}$$

where  $e^*$  is the effective dynamical charge,  $\xi_i$  the eigenvector, and  $\omega_i$  the frequency of the *i*th phonon mode. This indicates that larger ionic polarizability leads to higher dielectric constant. Since the lattice polarization splits the longitudinal optical (LO) and transverse optical (TO) phonon degeneracy in the long wavelength limit, the total static dielectric constant can be correlated to the high-frequency electronic dielectric constant through the Lyddane-Sachs-Teller relation

$$\frac{\mathcal{E}_0}{\mathcal{E}_{\infty}} = \prod_i \left( \frac{\omega_{LO}^i}{\omega_{TO}^i} \right)^2. \tag{4}$$

In many high-k materials such as  $TiO_2$  and  $SrTiO_3$ , some of the ratios of the frequencies of the LO and TO phonon pairs are about 2 or larger, and thus result in high dielectric constant. Since  $\varepsilon_0$  diverges when one of the TO mode frequencies goes to zero in Eq. (4), extremely high-k can be achieved through soft phonon driven lattice instability near the paraelectric to ferroelectric phase transition. The dielectric constant in this case follows the Curie-Weiss kind of temperature dependence

$$\varepsilon_{0} \propto \frac{1}{T - T_{C}},$$

where the Curie temperature  $T_c$  is 393K for BaTiO<sub>3</sub> and 0K for SrTiO<sub>3</sub>.

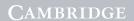

In addition to the high dielectric constant, the other basic requirement to the physical properties is a large energy gap that gives rise to reasonable conduction and valence band offsets to ensure low leakage current. However, certain compromise needs to be effected between high-k and large bandgap since the bandgap tends to decrease with increasing dielectric constant (see Fig. 1.1). Table 1.1 summarizes the bandgap and calculated band offsets between Si and various dielectrics by John Robertson of Cambridge University using a charge neutrality model. It can be seen again that SiO<sub>2</sub> and Al<sub>2</sub>O<sub>3</sub> have the largest bandgaps and band offsets, but smaller dielectric constants. On the other hand, the perovskite oxides usually have very high dielectric constants, but smaller energy gaps and band offsets, in particular, very small conduction band offsets. TiO<sub>2</sub> and Ta<sub>2</sub>O<sub>5</sub> have similar problem. Therefore, the "medium-k" oxides with reasonably wide gaps and band offsets are currently focussed upon as possible replacement materials of SiO<sub>2</sub> as gate dielectrics.

Although there is a list of candidates that meet the "medium-k" requirements in terms of the dielectric constant and band offsets, to integrate them successfully into the current CMOS

978-1-107-41219-4 - Materials Research Society Symposium Proceedings: Volume 670:

Gate Stack and Silicide Issues in Silicon Processing II

Editors: S. A. Campbell, L. A. Clevenger, P. B. Griffin and C. C. Hobbs

Excerpt

More information

process flows still posts tremendous challenges. Key issues such as thermal stability, interface chemistry and diffusion resistance need to be resolved to ensure low leakage current  $(<1\text{mA/cm}^2\text{ at }\pm1\text{V})$  and electrical interface states  $(<1\text{x}10^{11}\text{cm}^{-2}\text{eV})$ , high electron and hole mobility in the channel as well as good reliability.

Figure 1. Band gap versus dielectric constant for potential candidates as gate dielectrics.

Table 1.1. Bandgap and calculated conduction band (CB) and valence band (VB) offsets for various dielectrics (taken from [2]).

| Material                       | Bandgap (eV) | CB Band Offset (eV) | VB Band Offset (eV) |

|--------------------------------|--------------|---------------------|---------------------|

| SiO <sub>2</sub>               | 9.0          | 3.5                 | 4.4                 |

| Si <sub>3</sub> N <sub>4</sub> | 5.3          | 2.4                 | 1.8                 |

| SrTiO <sub>3</sub>             | 3.3          | -0.1                | 2.3                 |

| PbTiO,                         | 3.4          | 0.6                 | 1.7                 |

| BaZrO <sub>3</sub>             | 5.3          | 0.8                 | 3.4                 |

| PbZrO,                         | 3.7          | 0.2                 | 2.4                 |

| Ta,O,                          | 4.4          | 0.36                | 2.9                 |

| SrBi,Ti,O,                     | 4.1          | 0.15                | 2.9                 |

| TiO,                           | 3.1          | 0.0                 | 2.0                 |

| ZrO,                           | 5.8          | 1.4                 | 3.3                 |

| HfO,                           | 6.0          | 1.5                 | 3.4                 |

| Al <sub>2</sub> O <sub>3</sub> | 8.8          | 2.8                 | 4.9                 |

| Y,O,                           | 6.0          | 2.3                 | 2.6                 |

| La,O,                          | 6.0          | 2.3                 | 2.6                 |

| ZrSiO₄                         | 6.0          | 1.5                 | 3.4                 |

| HfSiO₄                         | 6.0          | 1.5                 | 3.4                 |

Extensive efforts have been made to develop high-k gate oxides, including transitional metal oxides and silicates ( $Ta_2O_5$  [3],  $TiO_2$  [4],  $ZrO_2$  [5],  $HfO_2$  [6],  $HfSi_xO_y$  [7]), rare earth metal oxides ( $Gd_2O_3$  [8],  $Pr_2O_3$  [9]), and other oxides ( $Al_2O_3$  [10]). Perovskite-type oxides such as

978-1-107-41219-4 - Materials Research Society Symposium Proceedings: Volume 670:

Gate Stack and Silicide Issues in Silicon Processing II

Editors: S. A. Campbell, L. A. Clevenger, P. B. Griffin and C. C. Hobbs

Excerpt

More information

strontium titanate, SrTiO<sub>3</sub> (STO), with much higher dielectric constant have also attracted tremendous interest as alternative gate dielectrics [11, 12]. However, currently there is still no clear front runner for the next alternative gate dielectrics. This paper will present some of the characterization results on MBE STO, CVD HfO<sub>2</sub>, and ZrO<sub>2</sub> films on Si.

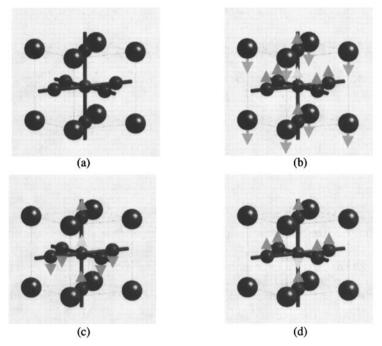

Figure 2. (a): Unit cell, (b): the lowest, (c): the second lowest, and (d): the highest  $F_{1u}$  modes of  $SrTiO_3$ . Ti atoms are at the body center, O atoms at face centers, and Sr atoms at corners.

## HIGH-K PEROVSKITE OXIDES: SrTiO3

Perovskite forms a family of compounds of formula ABO $_3$  that all have the same structure. This structure is strictly cubic (see Fig. 2) only for the non-ferroelectric phase above the Curie temperature. Three of the four 3-fold degenerate optical phonon modes, which contribute the most to the lattice dielectric response, are shown in Figs. 2(b), (c) and (d). In particular, the lowest mode goes soft with decreasing temperature and thus makes the dominant contribution to the dielectric constant and also triggers the phase transition. SrTiO $_3$  has a simple cubic crystal structure and a bulk k value of  $\sim 300$  at room temperature. Although the lattice constant of SrTiO $_3$  (a = 3.905 Å) is very different from that of Si (a = 5.431 Å), the lattice mismatch is fairly small ( $\sim 1.7\%$ ) with the STO unit cell rotated 45° around Si surface normal [001] axis to match the STO cell diagonal with the Si lattice constant.

The STO films studied in this work were deposited on up to 8" Si wafers by molecular beam epitaxy (MBE) with a base pressure of  $5x10^{-10}$  mbar. Metallic Sr was used to react with the native

978-1-107-41219-4 - Materials Research Society Symposium Proceedings: Volume 670:

Gate Stack and Silicide Issues in Silicon Processing II

Editors: S. A. Campbell, L. A. Clevenger, P. B. Griffin and C. C. Hobbs

Excerpt

More information

oxide on the Si wafer at temperatures greater than 750°C and under high vacuum. Using this process, a 2x1 surface reconstruction was consistently obtained [12]. The details for the film growth are described elsewhere [12]. The surface structure, growth rate and stoichiometry were monitored using in-situ Reflection High-Energy Electron Diffraction (RHEED).

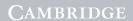

Figure 3. X-ray diffraction  $2\theta$  scan and electron diffraction pattern from a MBE STO film on Si.

Figure 3a displays the X-ray diffraction  $2\theta$  scan from a MBE film grown on Si. Only the diffraction peaks for the cubic lattices of STO and Si are seen, indicating that the STO film is oriented with the (001) axis parallel to the (001) axis of the Si substrate. Furthermore, the electron diffraction pattern from the film (Fig. 3b) shows that the diffraction pattern from the STO film (larger spots) is  $45^{\circ}$  rotated around the (001) axis with respect to that of the Si substrate (smaller spots) to minimize the lattice mismatch between the two.

978-1-107-41219-4 - Materials Research Society Symposium Proceedings: Volume 670:

Gate Stack and Silicide Issues in Silicon Processing II

Editors: S. A. Campbell, L. A. Clevenger, P. B. Griffin and C. C. Hobbs

Excerpt

More information

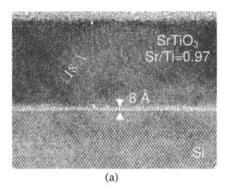

Figure 4. High-resolution TEM image of the interfacial region between MBE STO film and Si.

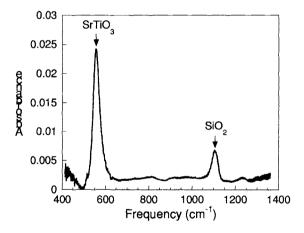

Figure 5. Infrared absorbance spectrum from a MBE STO film on Si. Both the highest-frequency TO peak in STO as well as the  $SiO_2$  peak from the interfacial layer were observed.

Since both the calculation (see Table I) and XPS measurement [13] showed about 0 eV conduction band offset between STO and Si, it is expected that the n-channel devices using a single STO dielectric layer may be very leaky. Therefore, one should engineer the band off set to minimize the leakage current. The first strategy is to add an interfacial layer with wider band gap, such as SrO, BaO [11] or SiO<sub>x</sub>. Actually, although STO can be grown directly on Si, a thin layer of interfacial SiO<sub>x</sub> is formed in most cases between STO and Si. This oxide layer can naturally serve as the buffer layer with much larger band offset. Figure 4 shows the high-resolution TEM (HRTEM) image of the interfacial region of a MBE STO film on Si. An amorphous interfacial layer of about 7 Å thick can be seen sandwiched between the single crystalline STO film and the

978-1-107-41219-4 - Materials Research Society Symposium Proceedings: Volume 670:

Gate Stack and Silicide Issues in Silicon Processing II

Editors: S. A. Campbell, L. A. Clevenger, P. B. Griffin and C. C. Hobbs

Excerpt

More information

Si substrate. High-resolution EELS mappings of similar samples using TEM indicated that the amorphous layer is silicon oxide [12]. The existence of the interfacial layer has also been revealed by infrared transmission measurements. Figure 5 displays the absorbance spectrum in the spectral range from 400 to 1400 cm<sup>-1</sup> from a MBE film on Si. Both the highest TO phonon peak from STO as well as a peak due to interfacial SiO<sub>2</sub> were observed.

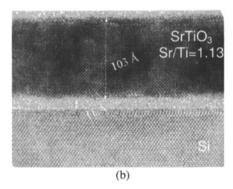

Figure 6. High-resolution TEM images of a stoichiometric STO film (a) and a Sr-rich STO film on Si.

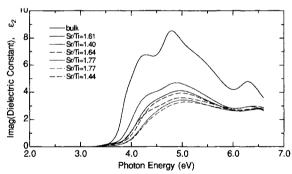

Figure 7. Imaginary part of the dielectric function versus photon energy derived from spectroscopic ellipsometry measurements on STO films with different Sr/Ti ratios in comparison with the bulk single crystal spectrum.

To further reduce the leakage current, efforts have also been directed to enlarge the STO band gap by changing the composition and to neutralize or trap oxygen vacancies in STO by Aldoping. The Sr to Ti ratio has been found rather sensitive to the growth parameters and Sr-rich films can be easily formed. TEM images show that the stoichiometric films are usually very uniform both in thickness and in cross section (Fig. 6a), while the Sr-rich films (Sr/Ti=1.13 measured by RBS) exhibit some non-uniform TEM contrast (Fig. 6b). This non-uniformity can be attributed to non-uniform composition distribution or local strains. The diffraction patterns

978-1-107-41219-4 - Materials Research Society Symposium Proceedings: Volume 670:

Gate Stack and Silicide Issues in Silicon Processing II

Editors: S. A. Campbell, L. A. Clevenger, P. B. Griffin and C. C. Hobbs

Excerpt

More information

obtained from the lattice fringes of different areas of the Sr-rich film revealed noticeable lattice constant changes across the film. At some locations, tetragonal lattice distortions were also observed. It is not clear at this point whether the local strains are directly related to possible microscopic compositional changes.

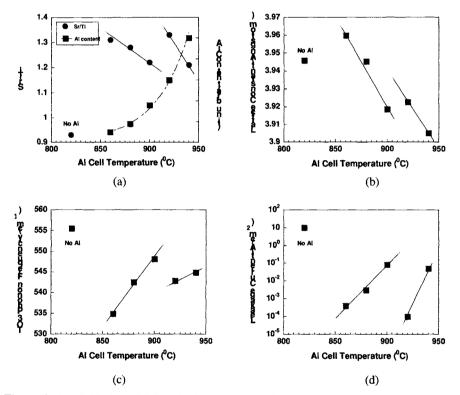

Figure 8. (a): Sr/Ti from RBS and Al content from SIMS, (b): average lattice constant from XRD, (c): the highest TO phonon frequency from FTIR, and (d): leakage current at  $\pm 1V$  from electrical measurement as a function of Al effusion cell temperature. The solid lines are guided by eye and the dash line in (a) is a fitted exponential curve.

The energy gaps of the Sr-rich films have been investigated using spectroscopic ellipsometry. Figure 7 shows the imaginary part,  $\varepsilon_2$ , of the complex dielectric functions of Sr-rich STO films of  $\sim 10$ nm thickness derived from the spectroscopic ellipsometry data using a general parametric oscillator model. Since a single layer was used to simulate the film as well as the interfacial oxide layer,  $\varepsilon_2$  for the thin films is considerably reduced by the interfacial SiO<sub>x</sub> that has no absorption in this energy range because of its much larger band gap. Further decrease in the absorption with increasing Sr/Ti results from the decrease in the density of states of the STO conduction band, which is mainly made up of Ti 3d states. It is very interesting to notice from